- Panel DL 2203C

- Panel DL 2203D

- Panel DL 2203S

- Jumper

3. Rangkaian Simulasi[Kembali]

4. Prinsip Kerja Rangkaian[Kembali

J-K Flip Flop

Input dan Output

- J dan K: Input data yang mengontrol perubahan keadaan output.

- Clock (CLK): Sinyal clock yang menandai waktu terjadinya perubahan keadaan.

- Q dan Q' (not Q): Output yang saling komplemen.

Cara Kerja Dasar

- Keadaan Stabil: Jika J dan K sama-sama 0, maka output Q tidak akan berubah, terlepas dari perubahan sinyal clock.

- Perubahan Keadaan: Perubahan keadaan output Q akan terjadi pada saat tepi naik atau tepi turun sinyal clock, tergantung pada jenis J-K flip-flop (positive edge-triggered atau negative edge-triggered).

- Tabel Kebenaran: Tabel kebenaran J-K flip-flop menunjukkan hubungan antara input J, K, dan keadaan output Q setelah terjadinya pulsa clock.

Penjelasan Tabel:

- J=0, K=0: Output tidak berubah (hold).

- J=0, K=1: Output menjadi 0 (reset).

- J=1, K=0: Output menjadi 1 (set).

- J=1, K=1: Output bertoggle (berubah ke kebalikannya).

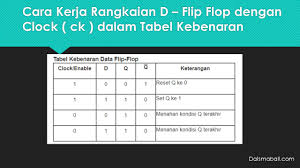

D-Flip Flop

D Flip-flop merupakan salah satu jenis flip-flop yang dibangun dengan menggunakan flip-flop R-S. Namun pada D Flip-flop inputan R diberi gerbang NOT. Arus mengalir dari power ke B1 dan ke kaki set. Arus mengalir ke B0 dan ke input R. Pada bagian D dan CLK tidak dihubungkan dan ini disebut juga dengan kondisi dont care dan tidak memberi pengaruh ke output.

Cara Kerja Dasar

- Input Data (D): Data yang ingin disimpan. Nilai D dapat berupa 0 atau 1.

- Clock (CLK): Sinyal clock yang menandai waktu terjadinya perubahan keadaan.

- Output (Q): Nilai bit yang sedang disimpan.

Proses Kerja:

- Keadaan Stabil: Selama sinyal clock tidak aktif, nilai output Q akan mempertahankan nilai sebelumnya.

- Perubahan Keadaan: Ketika sinyal clock mencapai tepi aktif (bisa tepi naik atau tepi turun, tergantung jenis D flip-flop), nilai input data D akan disalin secara langsung ke output Q. Dengan kata lain, Q akan mengambil nilai yang sama dengan D pada saat tepi clock aktif.

Keterangan:

- ↑: Tepi naik sinyal clock

- ↓: Tepi turun sinyal clock

- Q(t+1): Nilai output Q setelah terjadinya tepi clock

Tidak ada komentar:

Posting Komentar